# PROSLIC® PROGRAMMABLE CMOS SLIC/CODEC WITH RINGING/BATTERY VOLTAGE GENERATION

#### **Features**

- 100% programmable global solution

- Performs all BORSCHT functions

- DC-DC controller provides tracking battery from a 3.3–35V input (Si3210)

- Minimizes power in all modes

- Dynamic 0 to –94.5 V output

- Choice of inductor (low cost) or transformer (high efficiency)

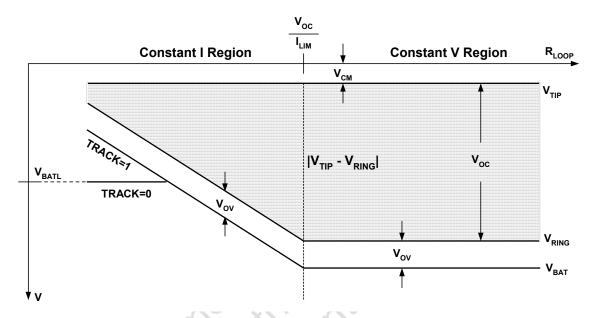

- Programmable line-feed parameters

- 2-wire AC impedance and hybrid

- Constant current feed (20 to 41 mA)

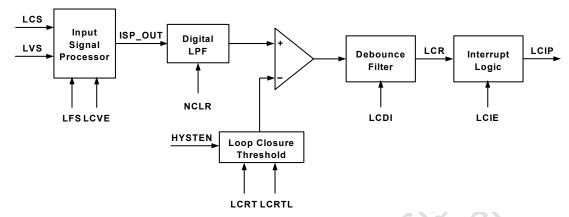

- Loop closure and ring trip thresholds and filtering

- Internal balanced ringing up to 90V<sub>PK</sub>

- 5 REN up to 4 kft; 3 REN up to 8 kft

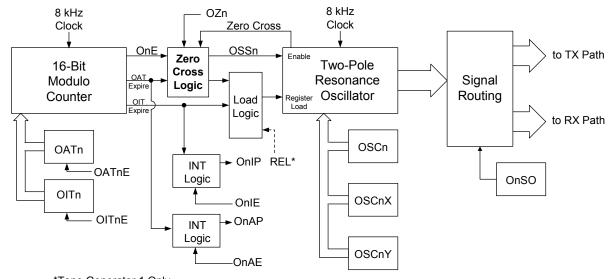

- Programmable frequency, amplitude, cadence, and wave shape

- Programmable audio processing

- DTMF encoding and decoding

- 12 kHz/16 kHz pulse metering

- Phase-continuous FSK (caller ID)

- Dual tone generators

- μ-Law/A-Law and linear PCM audio

- Extensive test and diagnostic features

- Multiple loopback test modes

- DC line V/I measurements

- Supports GR-909 MLT

- Comprehensive design tools

- Reference schematic and PCB layout

- ProSLIC API abstracts SLIC functions, minimizing software development

- RoHS-compliant packages

- SPI and PCM bus digital interfaces

- Fixed Wireless (cellular) Terminals

- Terminal Adapters

- PBX/IP-PBX/Key telephone systems

- Voice-over-IP Systems:

- DSL/EMTAs/FTTx

- WiMax/LTE

### **Description**

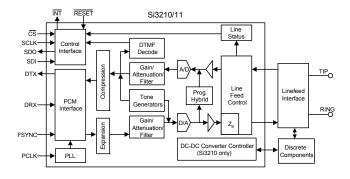

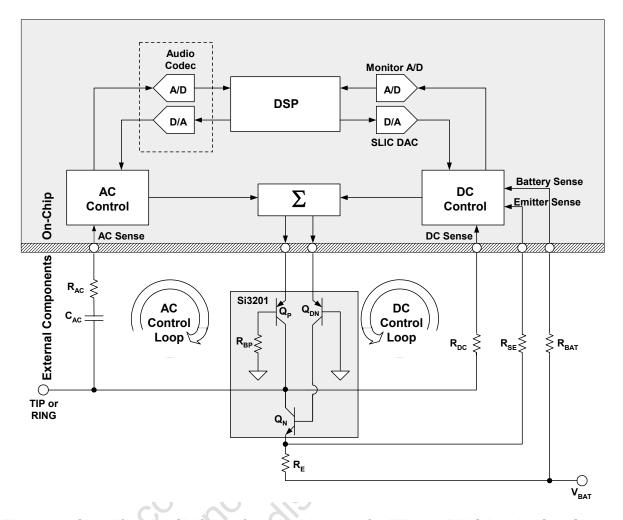

The Si3210/11 ProSLIC® chipset provides a complete analog telephone interface ideal for customer premise equipment (CPE). It integrates a subscriber line interface circuit (SLIC), voice codec, and battery generation (Si3210) or battery selection (Si3211) into a single CMOS integrated circuit. The battery supply continuously adapts its output voltage to minimize power dissipation and enables the entire circuit to be powered from a single 3.3 or 5 V supply (Si3210). The CMOS ProSLIC interfaces to the line through either the Si3201 Line-feed IC or a discrete line-feed circuit.

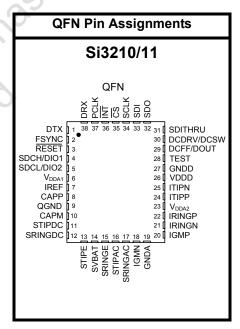

Si3210/11 features include software-configurable 5 REN internal ringing up to 90 VPK, DTMF generation and decoding, Caller ID generation, and a comprehensive set of telephony signaling capabilities for global operation with a single hardware solution. The Si3210/11 is packaged in a 38-pin QFN or TSSOP, and the Si3201 is packaged in a thermally-enhanced 16-pin SOIC.

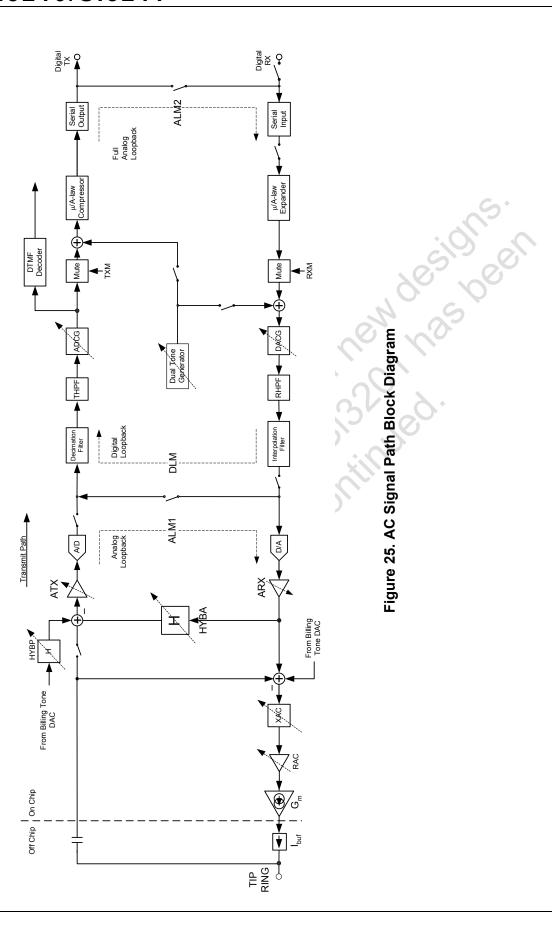

### **Functional Block Diagram**

U.S. Patent #6,567,521

U.S. Patent #6,812,744

# Si3210/Si3211

# TABLE OF CONTENTS

| 1. Electrical Specifications                                                                   | 3   |

|------------------------------------------------------------------------------------------------|-----|

| 2. Functional Description                                                                      |     |

| 2.1. Linefeed Interface                                                                        |     |

| 2.2. Battery Voltage Generation and Switching                                                  | 36  |

| 2.3. Tone Generation                                                                           |     |

| 2.4. Ringing Generation                                                                        | 43  |

| 2.5. Pulse Metering Generation                                                                 |     |

| 2.6. DTMF Detection                                                                            | 49  |

| 2.6. DTMF Detection                                                                            | 49  |

| 2.8. Two-Wire Impedance Matching                                                               | 52  |

| 2.9. Clock Generation                                                                          | 52  |

| 2.10. Interrupt Logic                                                                          | 52  |

| 2.10. Interrupt Logic                                                                          | 53  |

| 2 12 PCM Interface                                                                             | 56  |

| 2.13. Companding                                                                               | 57  |

| 2.13. Companding                                                                               | 60  |

| 4. Indirect Registers                                                                          | 118 |

| 4.1. DTMF Decoding                                                                             | 118 |

| 4. Indirect Registers       4.1. DTMF Decoding         4.2. Oscillators       4.2. Oscillators | 120 |

| 4.3 Digital Programmable Gain/Attenuation                                                      | 122 |

| 4.4. SLIC Control                                                                              | 123 |

| 4.5. FSK Control                                                                               | 125 |

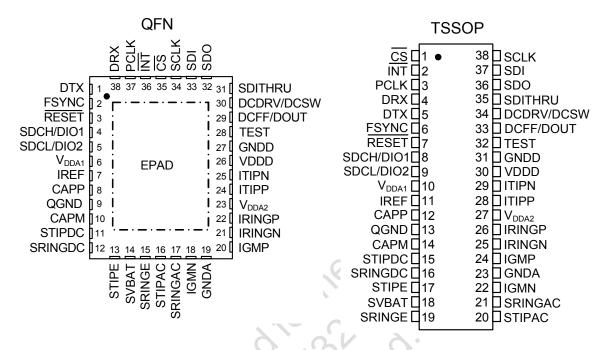

| 5. Pin Descriptions: Si3210/11                                                                 | 126 |

| 6 Pin Descriptions: Si3201                                                                     | 120 |

| 7. Ordering Guide                                                                              | 130 |

| 8. Package Outlines and PCB Land Patterns                                                      |     |

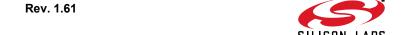

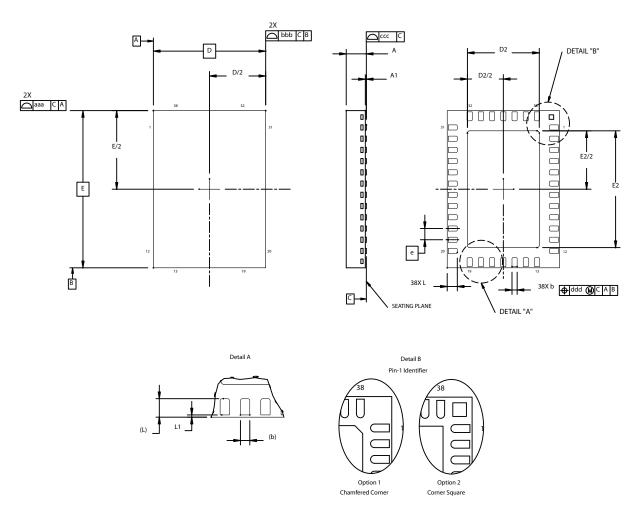

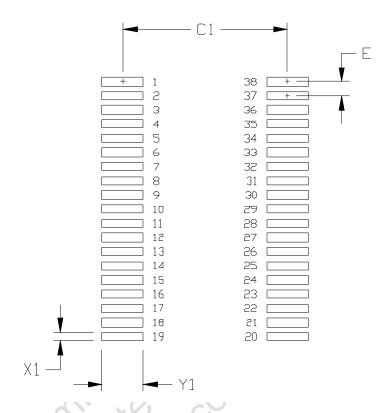

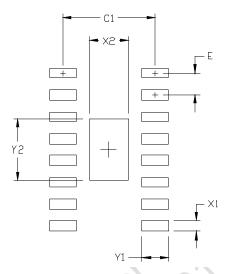

| 8.1. 38-Pin QFN                                                                                | 132 |

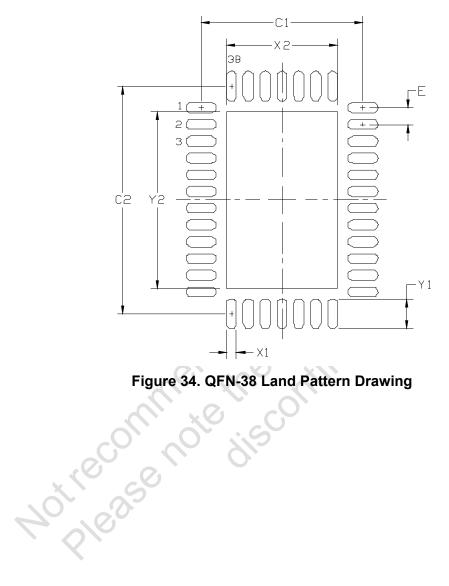

| 8.2. 38-Pin TSSOP                                                                              | 136 |

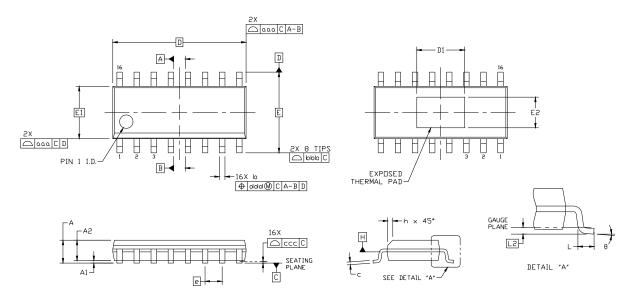

| 8.3. 16-Pin ESOIC                                                                              |     |

| 9. Product Identification                                                                      | 140 |

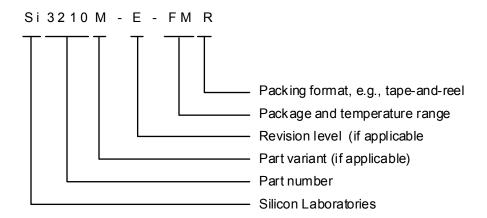

| 9.1. Ordering Part Number                                                                      | 140 |

| 9.2. Marking Part Number                                                                       | 140 |

| 10. Package Marking (Top Mark)                                                                 | 141 |

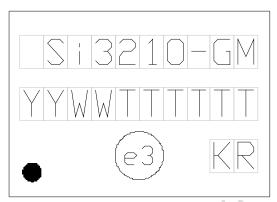

| 10.1. QFN Package                                                                              | 141 |

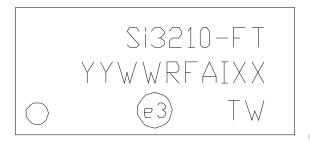

| 10.2. TSSOP Package                                                                            |     |

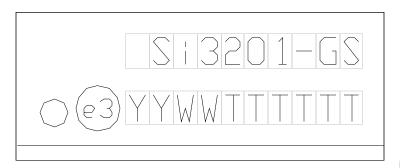

| 10.3. SOIC (Si3201) Package                                                                    |     |

| Document Change List                                                                           |     |

| Contact Information                                                                            | 1/1 |

# 1. Electrical Specifications

Table 1. Absolute Maximum Ratings and Thermal Information 1

| Parameter                                        | Symbol                                                   | Value                                 | Unit |  |  |  |  |  |  |

|--------------------------------------------------|----------------------------------------------------------|---------------------------------------|------|--|--|--|--|--|--|

| Si3210/11                                        |                                                          |                                       |      |  |  |  |  |  |  |

| DC Supply Voltage                                | V <sub>DDD</sub> , V <sub>DDA1</sub> , V <sub>DDA2</sub> | -0.5 to 6.0                           | V    |  |  |  |  |  |  |

| Input Current, Digital Input Pins                | I <sub>IN</sub>                                          | ±10                                   | mA   |  |  |  |  |  |  |

| Digital Input Voltage                            | V <sub>IND</sub>                                         | -0.3 to (V <sub>DDD</sub> + 0.3)      | V    |  |  |  |  |  |  |

| Operating Temperature Range <sup>2</sup>         | T <sub>A</sub>                                           | -40 to 100                            | С    |  |  |  |  |  |  |

| Storage Temperature Range                        | T <sub>STG</sub>                                         | -40 to 150                            | С    |  |  |  |  |  |  |

| TSSOP-38 Thermal Resistance, Typical             | $\theta_{JA}$                                            | 70                                    | C/W  |  |  |  |  |  |  |

| QFN-38 Thermal Resistance, Typical               | $\theta_{JA}$                                            | 35                                    | C/W  |  |  |  |  |  |  |

| Continuous Power Dissipation <sup>2</sup>        | P <sub>D</sub>                                           | 0.7                                   | W    |  |  |  |  |  |  |

|                                                  | Si3201                                                   |                                       |      |  |  |  |  |  |  |

| DC Supply Voltage                                | $V_{DD}$                                                 | -0.5 to 6.0                           | V    |  |  |  |  |  |  |

| Battery Supply Voltage                           | V <sub>BAT</sub>                                         | -104                                  | V    |  |  |  |  |  |  |

| Input Voltage: TIP, RING, SRINGE, STIPE pins     | V <sub>INHV</sub>                                        | $(V_{BAT} - 0.3)$ to $(V_{DD} + 0.3)$ | V    |  |  |  |  |  |  |

| Input Voltage: ITIPP, ITIPN, IRINGP, IRINGN pins | V <sub>IN</sub>                                          | -0.3 to (V <sub>DD</sub> + 0.3)       | V    |  |  |  |  |  |  |

| Operating Temperature Range <sup>2</sup>         | T <sub>A</sub>                                           | -40 to 100                            | С    |  |  |  |  |  |  |

| Storage Temperature Range                        | T <sub>STG</sub>                                         | -40 to 150                            | С    |  |  |  |  |  |  |

| SOIC-16 Thermal Resistance, Typical <sup>3</sup> | $\theta_{JA}$                                            | 55                                    | C/W  |  |  |  |  |  |  |

|                                                  | Б                                                        | 0.8 at 70 °C                          | 14/  |  |  |  |  |  |  |

| Continuous Power Dissipation <sup>2</sup>        | P <sub>D</sub>                                           | 0.6 at 85 °C                          | W    |  |  |  |  |  |  |

| Notes                                            | •                                                        | L                                     |      |  |  |  |  |  |  |

# Notes:

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Operation above 125 °C junction temperature may degrade device reliability.

- 3. Thermal resistance assumes a multi-layer PCB with the exposed pad soldered to a topside PCB pad.

**Table 2. Recommended Operating Conditions**

| Parameter                | Symbol                                                     | Test Condition                       | Min* | Тур            | Max* | Unit |

|--------------------------|------------------------------------------------------------|--------------------------------------|------|----------------|------|------|

| Ambient Temperature      | T <sub>A</sub>                                             | F-grade                              | 0    | 25             | 70   | °C   |

| Ambient Temperature      | T <sub>A</sub>                                             | G-grade                              | -40  | 25             | 85   | °C   |

| Si3210/11 Supply Voltage | V <sub>DDD</sub> ,V <sub>DDA1</sub> ,<br>V <sub>DDA2</sub> |                                      | 3.13 | 3.3/5.0        | 5.25 | V    |

| Si3201 Supply Voltage    | $V_{DD}$                                                   |                                      | 3.13 | 3.3/5.0        | 5.25 | V    |

| Si3201 Battery Voltage   | $V_{BAT}$                                                  | V <sub>BATH</sub> = V <sub>BAT</sub> | -96  | √ <del>,</del> | -10  | V    |

<sup>\*</sup>Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

Product specifications are only guaranteed for the typical application circuit (including component tolerances).

**Table 3. AC Characteristics**

$(V_{DDA}, V_{DDD} = 3.13 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70 \,^{\circ}\text{C} \text{ for F-Grade}, -40 \text{ to } 85 \,^{\circ}\text{C} \text{ for G-Grade})$

| Parameter                                                       | Test Condition                                                                | Min        | Тур  | Max         | Unit            |  |  |  |  |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------|------------|------|-------------|-----------------|--|--|--|--|--|--|

| TX/RX Performance                                               |                                                                               |            |      |             |                 |  |  |  |  |  |  |

| Overload Level                                                  | THD = 1.5%                                                                    | 2.5        | _    | _           | V <sub>PK</sub> |  |  |  |  |  |  |

| Single Frequency Distortion <sup>1</sup>                        | 2-wire – PCM or<br>PCM – 2-wire:<br>200 Hz–3.4 kHz                            | 110        | _    | <b>–4</b> 5 | dB              |  |  |  |  |  |  |

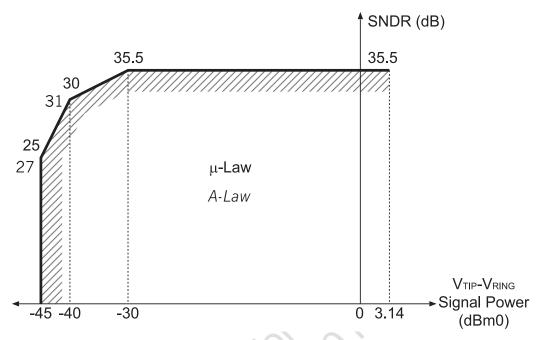

| Signal-to-(Noise + Distortion) Ratio <sup>2</sup>               | 200 Hz to 3.4 kHz<br>D/A or A/D 8-bit<br>Active off-hook, and OHT,<br>any ZAC | Figure 1   | _    | _           |                 |  |  |  |  |  |  |

| Audio Tone Generator<br>Signal-to-Distortion Ratio <sup>2</sup> | 0 dBm0, Active off-hook,<br>and OHT, any Zac                                  | 45         | _    | _           | dB              |  |  |  |  |  |  |

| Intermodulation Distortion                                      |                                                                               | _          | _    | <b>-45</b>  | dB              |  |  |  |  |  |  |

| Gain Accuracy <sup>2</sup>                                      | 2-wire to PCM, 1014 Hz                                                        | -0.5       | 0    | 0.5         | dB              |  |  |  |  |  |  |

| 010                                                             | PCM to 2-wire, 1014 Hz                                                        | -0.5       | 0    | 0.5         | dB              |  |  |  |  |  |  |

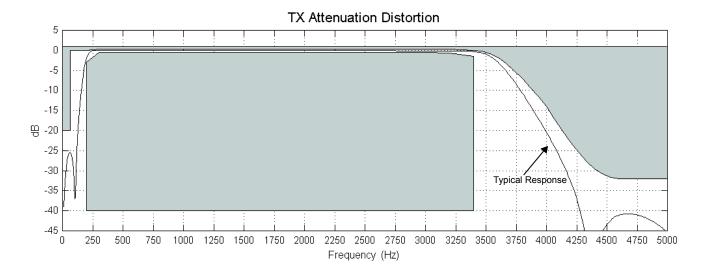

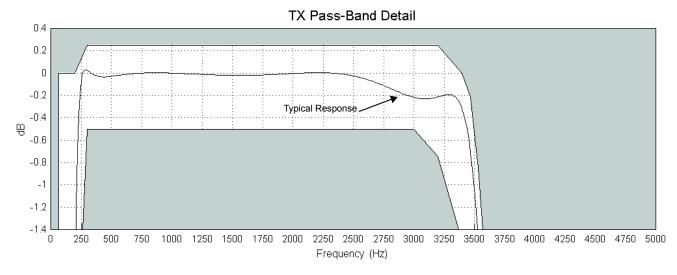

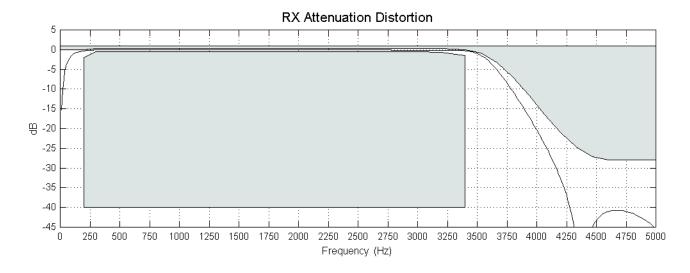

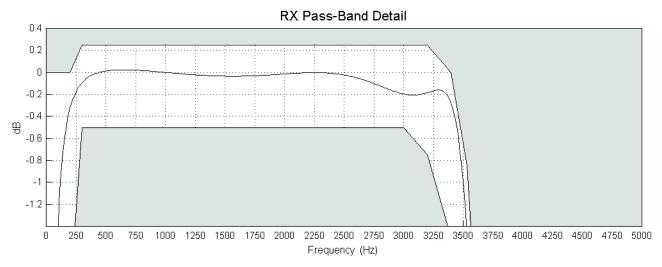

| Gain Accuracy over Frequency                                    |                                                                               | Figure 3,4 | _    | _           |                 |  |  |  |  |  |  |

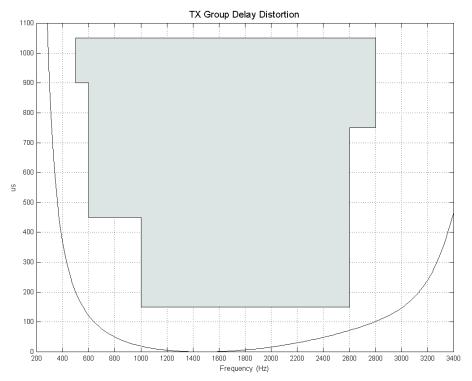

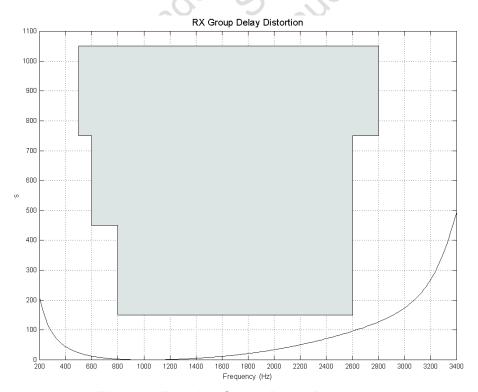

| Group Delay over Frequency                                      |                                                                               | Figure 5,6 | _    | _           |                 |  |  |  |  |  |  |

|                                                                 | 1014 Hz sine wave,<br>reference level –10 dBm<br>signal level:                |            |      |             |                 |  |  |  |  |  |  |

| Gain Tracking <sup>3</sup>                                      | 3 to -37 dB                                                                   | -0.25      | _    | 0.25        | dB              |  |  |  |  |  |  |

|                                                                 | −37 to −50 dB                                                                 | -0.5       | _    | 0.5         | dB              |  |  |  |  |  |  |

|                                                                 | –50 to –60 dB                                                                 | -1.0       | _    | 1.0         | dB              |  |  |  |  |  |  |

| Round-Trip Group Delay                                          | at 1000 Hz                                                                    | _          | 1100 | _           | μs              |  |  |  |  |  |  |

| Gain Step Accuracy                                              | −6 to +6 dB                                                                   | -0.017     | _    | 0.017       | dB              |  |  |  |  |  |  |

| Gain Variation with Temperature                                 | All gain settings                                                             | -0.25      | _    | 0.25        | dB              |  |  |  |  |  |  |

| Gain Variation with Supply                                      | $V_{DDA} = V_{DDA} = 3.3/5 \text{ V } \pm 5\%$                                | -0.1       | _    | 0.1         | dB              |  |  |  |  |  |  |

**Table 3. AC Characteristics (Continued)**

$(V_{DDA}, V_{DDD} = 3.13 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70 ^{\circ}\text{C} \text{ for F-Grade}, -40 \text{ to } 85 ^{\circ}\text{C} \text{ for G-Grade})$

| Parameter                        | Test Condition                                                                            | Min         | Тур            | Max         | Unit                       |

|----------------------------------|-------------------------------------------------------------------------------------------|-------------|----------------|-------------|----------------------------|

| 2-Wire Return Loss               | 200 Hz to 3.4 kHz                                                                         | 30          | 35             | _           | dB                         |

| Transhybrid Balance              | 300 Hz to 3.4 kHz                                                                         | 30          | _              | _           | dB                         |

|                                  | Noise Performance                                                                         |             | •              |             |                            |

|                                  | C-Message Weighted                                                                        | _           | _              | 15          | dBrnC                      |

| Idle Channel Noise <sup>4</sup>  | Psophometric Weighted                                                                     | _           |                | <b>–</b> 75 | dBmP                       |

|                                  | 3 kHz flat                                                                                | _           | V-5            | 18          | dBrn                       |

| PSRR from VDDA                   | RX and TX, DC to 3.4 kHz                                                                  | 40          | 0, $ 0$        | _           | dB                         |

| PSRR from VDDD                   | RX and TX, DC to 3.4 kHz                                                                  | 40          | -0,            | _           | dB                         |

| PSRR from VBAT                   | RX and TX, DC to 3.4 kHz                                                                  | 40          | VO.            | _           | dB                         |

|                                  | Longitudinal Performa                                                                     | nce         |                |             |                            |

|                                  | 200 Hz to 3.4 kHz, $\beta_{Q1,Q2} \ge$ 150, 1% mismatch                                   | 56          | 60             | _           | dB                         |

| Longitudinal to Metallic         | $\beta_{Q1,Q2} = 60 \text{ to } 240^5$                                                    | 43          | 60             | _           | dB                         |

| or PCM Balance                   | $\beta_{Q1,Q2} = 300 \text{ to } 800^5$                                                   | 53          | 60             | _           | dB                         |

|                                  | Using Si3201                                                                              | 53          | 60             | _           | dB                         |

| Metallic to Longitudinal Balance | 200 Hz to 3.4 kHz                                                                         | 40          | _              | _           | dB                         |

| Longitudinal Impedance           | 200 Hz to 3.4 kHz at TIP or<br>RING<br>Register selectable<br>ETBO/ETBA<br>00<br>01<br>10 |             | 33<br>17<br>17 | _<br>_<br>_ | $\Omega$ $\Omega$ $\Omega$ |

| Longitudinal Current per Pin     | Active off-hook 200 Hz to 3.4 kHz Register selectable ETBO/ETBA 00 01                     | _<br>_<br>_ | 4<br>8<br>12   | _<br>_<br>_ | mA<br>mA<br>mA             |

### Notes:

- 1. The input signal level should be 0 dBm0 for frequencies greater than 100 Hz. For 100 Hz and below, the level should be

- -10 dBm0. The output signal magnitude at any other frequency will be smaller than the maximum value specified.

- 2. Analog signal measured as  $V_{TIP} V_{RING}$ . Assumes ideal line impedance matching.

- 3. The quantization errors inherent in the  $\mu$ /A-law companding process can generate slightly worse gain tracking performance in the signal range of 3 to –37 dB for signal frequencies that are integer divisors of the 8 kHz PCM sampling rate.

- **4.** The level of any unwanted tones within the bandwidth of 0 to 4 kHz does not exceed –55 dBm.

- 5. Assumes normal distribution of betas.

6

Figure 1. Transmit and Receive Path SNDR

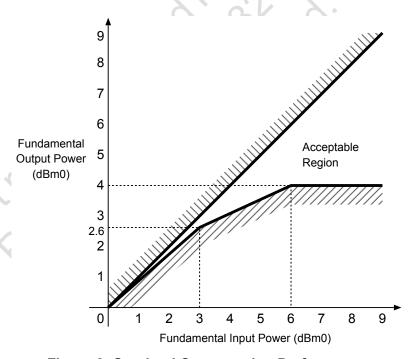

Figure 2. Overload Compression Performance

Figure 3. Transmit Path Frequency Response

Figure 4. Receive Path Frequency Response

**Figure 5. Transmit Group Delay Distortion**

Figure 6. Receive Group Delay Distortion

# Si3210/Si3211

**Table 4. Linefeed Characteristics**

(V<sub>DDA</sub>, V<sub>DDD</sub> = 3.13 to 5.25 V,  $T_A$  = 0 to 70°C for F-Grade, –40 to 85°C for G-Grade)

| Parameter                                             | Symbol              | Test Condition                                                                        | Min  | Тур         | Max  | Unit             |

|-------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------|------|-------------|------|------------------|

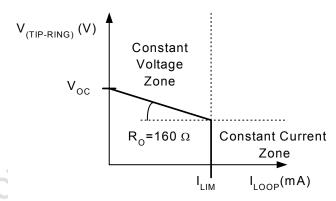

| Loop Resistance Range*                                | R <sub>LOOP</sub>   | See *Note.                                                                            | 0    | _           | 160  | Ω                |

| DC Loop Current Accuracy                              |                     | I <sub>LIM</sub> = 29 mA, ETBA = 4 mA                                                 | -10  | _           | 10   | %                |

| DC Open Circuit Voltage<br>Accuracy                   |                     | Active Mode; V <sub>OC</sub> = 48 V,<br>V <sub>TIP</sub> - V <sub>RING</sub>          | -4   | _           | 4    | V                |

| DC Differential Output<br>Resistance                  | $R_{DO}$            | I <sub>LOOP</sub> < I <sub>LIM</sub>                                                  | _    | <b>1</b> 60 |      | Ω                |

| DC Open Circuit Voltage—<br>Ground Start              | V <sub>OCTO</sub>   | $I_{RING} < I_{LIM}$ ; $V_{RING}$ wrt ground $V_{OC} = 48 \text{ V}$                  | -4   | 30          | 4    | V                |

| DC Output Resistance—<br>Ground Start                 | R <sub>ROTO</sub>   | I <sub>RING</sub> <i<sub>LIM; RING to ground</i<sub>                                  | 37-  | 160         | _    | Ω                |

| DC Output Resistance—<br>Ground Start                 | R <sub>TOTO</sub>   | TIP to ground                                                                         | 150  | _           | _    | kΩ               |

| Loop Closure/Ring Ground<br>Detect Threshold Accuracy |                     | I <sub>THR</sub> = 11.43 mA                                                           | -20  | _           | 20   | %                |

| Ring Trip Threshold<br>Accuracy                       |                     | I <sub>THR</sub> = 40.64 mA                                                           | -10  | _           | 10   | %                |

| Ring Trip Response Time                               |                     | User Programmable Register 70 and Indirect Register 36                                | _    | _           | _    |                  |

| Ring Amplitude                                        | V <sub>TR</sub>     | 5 REN load; sine wave;<br>R <sub>LOOP</sub> = 160 $\Omega$ , V <sub>BAT</sub> = -75 V | 44   | _           | _    | V <sub>rms</sub> |

| Ring DC Offset                                        | Ros                 | Programmable in Indirect<br>Register 19                                               | 0    | _           | _    | V                |

| Trapezoidal Ring Crest<br>Factor Accuracy             |                     | Crest factor = 1.3                                                                    | 05   | _           | .05  |                  |

| Sinusoidal Ring Crest<br>Factor                       | R <sub>CF</sub>     |                                                                                       | 1.35 | _           | 1.45 |                  |

| Ringing Frequency Accuracy                            |                     | f = 20 Hz                                                                             | -1   | _           | 1    | %                |

| Ringing Cadence Accuracy                              |                     | Accuracy of ON/OFF Times                                                              | -50  | _           | 50   | ms               |

| Calibration Time                                      |                     | ↑CAL to ↓CAL Bit                                                                      | _    |             | 600  | ms               |

| Power Alarm Threshold<br>Accuracy                     |                     | At Power Threshold = 300 mW                                                           | -25  | _           | 25   | %                |

| *Note: DC resistance round tr                         | ip; 160 $\Omega$ co | orresponds to 2 kft, 26 gauge AW                                                      | G.   |             |      |                  |

# **Table 5. Monitor ADC Characteristics**

( $V_{DDA}$ ,  $V_{DDD}$  = 3.13 to 5.25 V,  $T_A$  = 0 to 70 °C for F-Grade, –40 to 85 °C for G-Grade)

| Parameter                                    | Symbol | Test Condition | Min  | Тур          | Max | Unit |

|----------------------------------------------|--------|----------------|------|--------------|-----|------|

| Differential Nonlinearity (6-bit resolution) | DNLE   |                | -1/2 | _            | 1/2 | LSB  |

| Integral Nonlinearity<br>(6-bit resolution)  | INLE   |                | -1   | _            | 1   | LSB  |

| Gain Error (Voltage)                         |        |                | _    | 3.           | 10  | %    |

| Gain Error (Current)                         |        |                | (    | <u>)</u> – ( | 20  | %    |

# Table 6. Si321x DC Characteristics, $V_{DDA} = V_{DDD} = 5.0 \text{ V}$

$(V_{DDA}, V_{DDD}$  = 4.75 to 5.25 V,  $T_A$  = 0 to 70 °C for F-Grade, –40 to 85 °C for G-Grade)

| Parameter                 | Symbol          | Test Condition                                                                                             | Min                    | Тур | Max                    | Unit |

|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

| High Level Input Voltage  | V <sub>IH</sub> |                                                                                                            | 0.7 x V <sub>DDD</sub> | _   | _                      | V    |

| Low Level Input Voltage   | V <sub>IL</sub> | 160.00                                                                                                     | ) _                    | _   | 0.3 x V <sub>DDD</sub> | V    |

| High Level Output Voltage | V <sub>OH</sub> | DIO1,DIO2,SDITHRU:<br>I <sub>O</sub> = -4 mA SDO,<br>DTX:I <sub>O</sub> = -8 mA                            | V <sub>DDD</sub> – 0.6 | _   | _                      | V    |

|                           |                 | DOUT: I <sub>O</sub> = -40 mA                                                                              | V <sub>DDD</sub> – 0.8 | _   |                        | V    |

| Low Level Output Voltage  | V <sub>OL</sub> | DIO1,DIO2,DOUT,SDITHRU:<br>$I_O = 4 \text{ mA}$<br>SDO, $\overline{\text{INT}}$ ,DTX: $I_O = 8 \text{ mA}$ | _                      | _   | 0.4                    | V    |

| Input Leakage Current     | l <sub>L</sub>  | (, 0,                                                                                                      | -10                    | _   | 10                     | μΑ   |

# Table 7. Si321x DC Characteristics, $V_{DDA} = V_{DDD} = 3.3 \text{ V}$

$(V_{DDA}, V_{DDD}$  = 3.13 to 3.47 V,  $T_A$  = 0 to 70 °C for F-Grade, -40 to 85 °C for G-Grade)

| Parameter                 | Symbol          | Test Condition                                                                                             | Min                    | Тур | Max                    | Unit |

|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

| High Level Input Voltage  | $V_{IH}$        |                                                                                                            | 0.7 x V <sub>DDD</sub> | _   | _                      | V    |

| Low Level Input Voltage   | $V_{IL}$        |                                                                                                            | _                      | _   | 0.3 x V <sub>DDD</sub> | V    |

| High Level Output Voltage | V <sub>OH</sub> | DIO1,DIO2,SDITHRU: $I_O = -2 \text{ mA}$<br>SDO, DTX: $I_O = -4 \text{ mA}$                                | V <sub>DDD</sub> – 0.6 |     | _                      | V    |

|                           |                 | DOUT: I <sub>O</sub> = -40 mA                                                                              | V <sub>DDD</sub> – 0.8 | _   | _                      | V    |

| Low Level Output Voltage  | V <sub>OL</sub> | DIO1,DIO2,DOUT,SDITHRU:<br>$I_O = 2 \text{ mA}$<br>SDO, $\overline{\text{INT}}$ ,DTX: $I_O = 4 \text{ mA}$ | 1                      |     | 0.4                    | V    |

| Input Leakage Current     | Ι <sub>L</sub>  |                                                                                                            | -10                    | _   | 10                     | μΑ   |

**Table 8. Power Supply Characteristics**

(Unless otherwise noted,  $V_{DDA}$ ,  $V_{DDD}$ =3.13 to 5.25 V;  $T_A$ =0 to 70 $^{\circ}$ C for F-grade, –40 to 85 $^{\circ}$ C for G-grade)

| Parameter                                    | Symbol                          | Test Condition                                                                                                              | Typ <sup>1</sup> | Typ <sup>2</sup> | Max  | Unit |

|----------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------|------|

|                                              |                                 | Sleep ( <del>RESET</del> = 0),<br>V <sub>DDA</sub> =V <sub>DDD</sub> =3.13 to 3.465 V                                       | 0.1              | _                | 0.3  | mA   |

|                                              |                                 | Sleep ( $\overline{RESET}$ = 0),<br>V <sub>DDA</sub> =V <sub>DDD</sub> =4.75 to 5.25 V,<br>T <sub>A</sub> =0 to 70C/F-grade |                  | 0.1              | 0.3  | mA   |

|                                              |                                 | Sleep ( $\overline{RESET}$ = 0),<br>$V_{DDA} = V_{DDD} = 4.75$ to 5.25 V,<br>$T_A = -40$ to 85C/G-grade                     | 2                | 0.1              | 0.35 | mA   |

|                                              |                                 | Open                                                                                                                        | 33               | 42.8             | 49   | mA   |

| Power Supply Current,<br>Analog and Digital  | I <sub>A</sub> + I <sub>D</sub> | Active on-hook<br>ETBO = 4 mA, codec and Gm amplifier<br>powered down                                                       | 37               | 53               | 68   | mA   |

|                                              |                                 | Active OHT<br>ETBO = 4 mA                                                                                                   | 57               | 72               | 83   | mA   |

|                                              |                                 | Active off-hook<br>ETBA = 4 mA, I <sub>LIM</sub> = 20 mA                                                                    | 73               | 88               | 99   | mA   |

|                                              |                                 | Ground Start                                                                                                                | 36               | 47               | 55   | mA   |

|                                              |                                 | Ringing sinewave, REN = 1, V <sub>PK</sub> = 56 V                                                                           | 45               | 55               | 65   | mA   |

|                                              | ~(                              | Sleep mode, RESET = 0                                                                                                       | 100              | 100              | _    | μΑ   |

|                                              | I <sub>VDD</sub>                | Open (high impedance)                                                                                                       |                  | 100              | 1    | μΑ   |

|                                              |                                 | Active on-hook standby                                                                                                      | 110              | 110              | 1    | μΑ   |

| V <sub>DD</sub> Supply Current (Si3201)      |                                 | Forward/reverse active off-hook, no $I_{LOOP}$ ,<br>ETBO = 4 mA, $V_{BAT}$ = -24 V                                          | 1                | 1                | l    | mA   |

| die                                          | 5                               | Forward/reverse OHT, ETBO = 4 mA,<br>$V_{BAT} = -70 \text{ V}$                                                              | 1                | 1                | _    | mA   |

| 7000                                         |                                 | Sleep (RESET = 0)                                                                                                           | 0                | 0                | _    | mA   |

| , 0,                                         |                                 | Open (DCOF = 1)                                                                                                             | 0                | 0                |      | mA   |

|                                              |                                 | Active on-hook $V_{OC}$ = 48 V, ETBO = 4 mA                                                                                 | 3                | 3                | l    | mA   |

| V <sub>BAT</sub> Supply Current <sup>3</sup> | I <sub>BAT</sub>                | Active OHT<br>ETBO = 4 mA                                                                                                   | 11               | 11               |      | mA   |

|                                              |                                 | Active off-hook<br>ETBA = 4 mA, I <sub>LIM</sub> = 20 mA                                                                    | 30               | 30               | _    | mA   |

|                                              |                                 | Ground Start                                                                                                                | 2                | 2                |      | mA   |

|                                              |                                 | Ringing: $V_{PK\_RING} = 56 V_{PK}$ ,<br>Sinewave ringing: REN = 1                                                          | 5.5              | 5.5              |      | mA   |

| V <sub>BAT</sub> Supply Slew Rate            |                                 | When using Si3201                                                                                                           | _                | _                | 10   | V/µs |

# **Table 8. Power Supply Characteristics (Continued)**

(Unless otherwise noted, V<sub>DDA</sub>, V<sub>DDD</sub>=3.13 to 5.25 V; T<sub>A</sub>=0 to 70°C for F-grade, –40 to 85°C for G-grade)

| Parameter Symbol Test Condition Typ <sup>1</sup> Typ <sup>2</sup> Max Un | Parameter | Symbol | Test Condition |  | Typ <sup>2</sup> | Max | Unit |

|--------------------------------------------------------------------------|-----------|--------|----------------|--|------------------|-----|------|

|--------------------------------------------------------------------------|-----------|--------|----------------|--|------------------|-----|------|

#### Notes:

- **1.**  $V_{DDD}$ ,  $V_{DDA} = 3.3 \text{ V}$ .

- **2.**  $V_{DDD}$ ,  $V_{DDA} = 5.25 V$ .

- 3.  $I_{BAT}$  = current from  $V_{BAT}$  (the large negative supply). For a switched-mode power supply regulator efficiency of 71%, the user can calculate the regulator current consumption as  $I_{BAT}$  x  $V_{BAT}/(0.71 \text{ x V}_{DC})$ .

# Table 9. Switching Characteristics (General Inputs)<sup>1</sup>

$V_{DDA} = V_{DDA} = 3.13$  to 5.25 V,  $T_A = 0$  to 70 °C for F-Grade, –40 to 85 °C for G-Grade,  $C_L = 20$  pF)

| Parameter                      | Symbol          | Min | Тур            | Max | Unit |

|--------------------------------|-----------------|-----|----------------|-----|------|

| Rise Time, RESET               | t <sub>r</sub>  | 76  | , <del>~</del> | 20  | ns   |

| RESET Pulse Width <sup>2</sup> | t <sub>rl</sub> | 100 | 6-             | _   | ns   |

#### Notes:

- 1. All timing (except rise and fall time) is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ . Rise and fall times are referenced to the 20% and 80% levels of the waveform.

- 2. Additional initialization guidelines apply; see section 1.2 ProSLIC Initialization in AN35.

# Table 10. Switching Characteristics (SPI)

$V_{DDA} = V_{DDA} = 3.13$  to 5.25 V,  $T_A = 0$  to 70 °C for F-Grade, -40 to 85 °C for G-Grade,  $C_L = 20$  pF

| Parameter                                             | Symbol           | Test<br>Conditions | Min   | Тур | Max | Unit |

|-------------------------------------------------------|------------------|--------------------|-------|-----|-----|------|

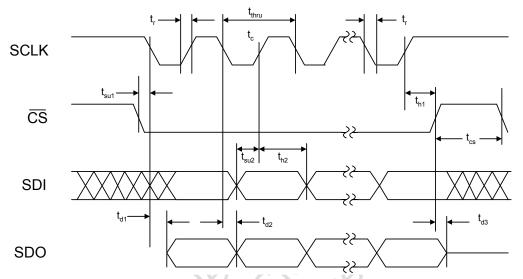

| Cycle Time SCLK                                       | t <sub>c</sub>   | CO.                | 0.062 | _   | _   | μs   |

| Rise Time, SCLK                                       | t <sub>r</sub>   | 5                  | _     | _   | 25  | ns   |

| Fall Time, SCLK                                       | t <sub>f</sub>   |                    | _     | _   | 25  | ns   |

| Delay Time, SCLK Fall to SDO Active                   | t <sub>d1</sub>  |                    | _     | _   | 20  | ns   |

| Delay Time, SCLK Fall to SDO<br>Transition            | t <sub>d2</sub>  |                    |       |     | 20  | ns   |

| Delay Time, CS Rise to SDO Tri-state                  | t <sub>d3</sub>  |                    |       |     | 20  | ns   |

| Setup Time, CS to SCLK Fall                           | t <sub>su1</sub> |                    | 25    |     | _   | ns   |

| Hold Time, CS to SCLK Rise                            | t <sub>h1</sub>  |                    | 20    |     | _   | ns   |

| Setup Time, SDI to SCLK Rise                          | t <sub>su2</sub> |                    | 25    |     | _   | ns   |

| Hold Time, SDI to SCLK Rise                           | t <sub>h2</sub>  |                    | 20    |     | _   | ns   |

| Delay Time between Chip Selects (Continuous SCLK)     | t <sub>cs</sub>  |                    | 440   | 1   | _   | ns   |

| Delay Time between Chip Selects (Non-continuous SCLK) | t <sub>cs</sub>  |                    | 220   | _   |     | ns   |

# **Table 10. Switching Characteristics (SPI)**

$V_{DDA} = V_{DDA} = 3.13$  to 5.25 V,  $T_A = 0$  to 70 °C for F-Grade, -40 to 85 °C for G-Grade,  $C_L = 20$  pF

| SDI to SDITHRU Propagation Delay                                                                                                                            | t <sub>d4</sub> |  | _ | 4 | 10 | ns |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|---|---|----|----|

| <b>Note:</b> All timing is referenced to the 50% level of the waveform. Input test levels are $V_{IH} = V_{DDD} - 0.4 \text{ V}$ , $V_{IL} = 0.4 \text{ V}$ |                 |  |   |   |    |    |

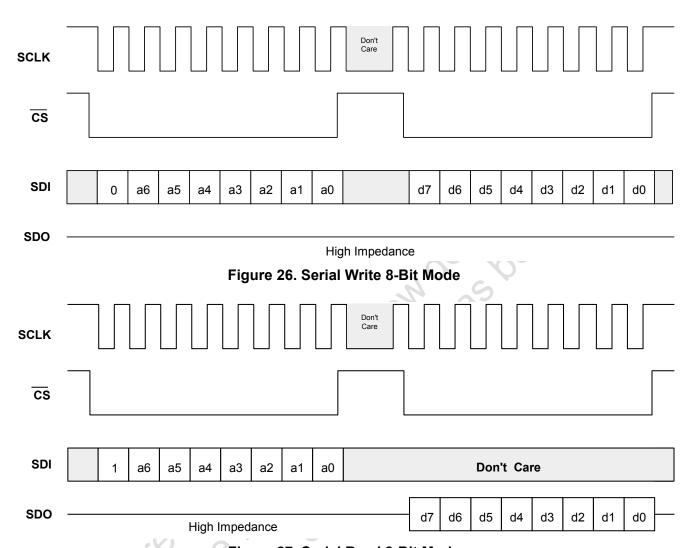

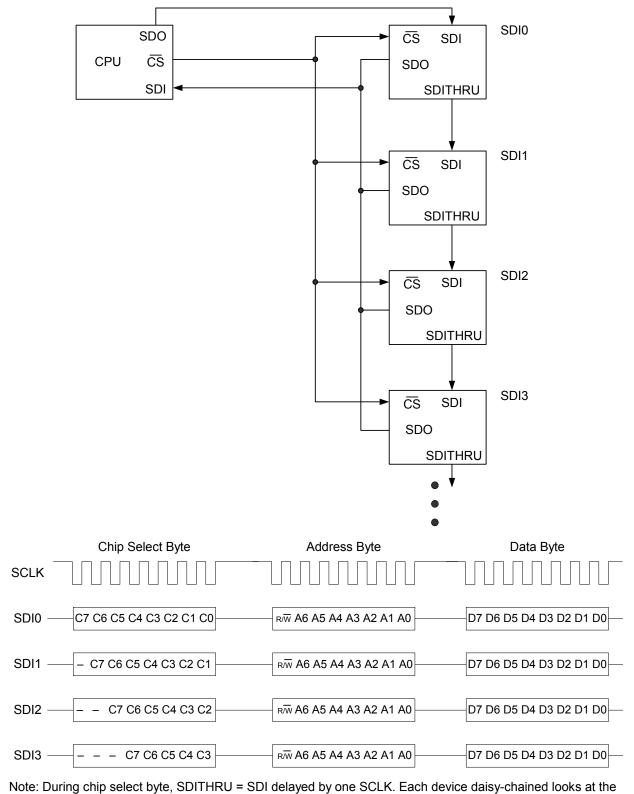

Figure 7. SPI Timing Diagram

Table 11. Switching Characteristics—PCM Highway Serial Interface

$V_D$  = 3.13 to 5.25 V,  $T_A$  = 0 to 70 °C for F-Grade, –40 to 85 °C for G-Grade,  $C_L$  = 20 pF

| Parameter                                           | Symbol              | Test<br>Conditions | Min <sup>1</sup> | Typ <sup>1</sup>   | Max <sup>1</sup> | Units |

|-----------------------------------------------------|---------------------|--------------------|------------------|--------------------|------------------|-------|

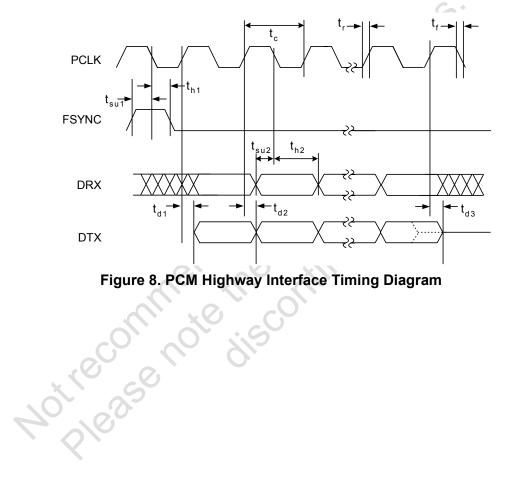

| -0 ()                                               |                     |                    | _                | 0.256              | _                | MHz   |

| PCLK Frequency                                      |                     |                    | _                | 0.512              | _                | MHz   |

| * 5                                                 |                     |                    | _                | 0.768 <sup>2</sup> | _                | MHz   |

| PCLK Frequency                                      | 1/t <sub>c</sub>    |                    | _                | 1.024              | _                | MHz   |

| 1 OLIX 1 requerity                                  | 17 C                |                    | _                | 1.536 <sup>2</sup> | _                | MHz   |

|                                                     |                     |                    | _                | 2.048              | _                | MHz   |

|                                                     |                     |                    | _                | 4.096              | _                | MHz   |

|                                                     |                     |                    |                  | 8.192              |                  | MHz   |

| PCLK Duty Cycle Tolerance                           | t <sub>dty</sub>    |                    | 40               | 50                 | 60               | %     |

| PCLK-to-FSYNC Jitter Tolerance                      | t <sub>jitter</sub> |                    | -120             |                    | 120              | ns    |

| Rise Time, PCLK                                     | t <sub>r</sub>      |                    |                  |                    | 25               | ns    |

| Fall Time, PCLK                                     | t <sub>f</sub>      |                    |                  |                    | 25               | ns    |

| Delay Time, PCLK Rise to DTX Active                 | t <sub>d1</sub>     |                    | _                | _                  | 20               | ns    |

| Delay Time, PCLK Rise to DTX<br>Transition          | t <sub>d2</sub>     |                    | l                |                    | 20               | ns    |

| Delay Time, PCLK Rise to DTX Tri-state <sup>3</sup> | t <sub>d3</sub>     |                    |                  |                    | 20               | ns    |

| Setup Time, FSYNC to PCLK Fall                      | t <sub>su1</sub>    |                    | 25               | _                  | _                | ns    |

| Hold Time, FSYNC to PCLK Fall                       | t <sub>h1</sub>     |                    | 20               | _                  | _                | ns    |

SILICON LARS

# Table 11. Switching Characteristics—PCM Highway Serial Interface

$V_D$  = 3.13 to 5.25 V,  $T_A$  = 0 to 70 °C for F-Grade, –40 to 85 °C for G-Grade,  $C_L$  = 20 pF

| Setup Time, DRX to PCLK Fall | t <sub>su2</sub> | 25 | - | _ | ns |

|------------------------------|------------------|----|---|---|----|

| Hold Time, DRX to PCLK Fall  | t <sub>h2</sub>  | 20 | _ | _ | ns |

### Notes:

- 1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} V_{I/O} = 0.4 \text{ V}$ .

- 2. Not a valid PCLK frequency for GCI mode.

- 3. Specification applies to PCLK fall to DTX tri-state when that mode is selected (TRI = 0).

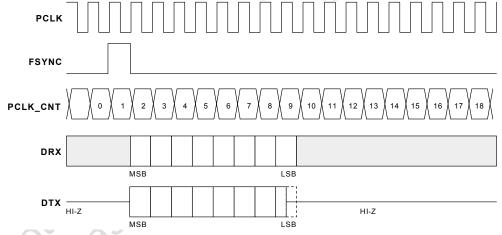

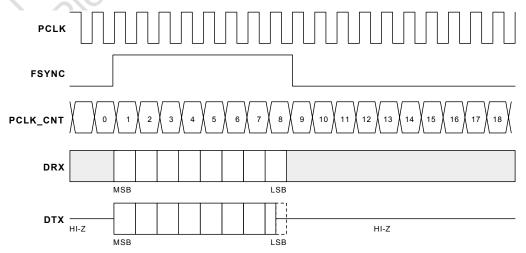

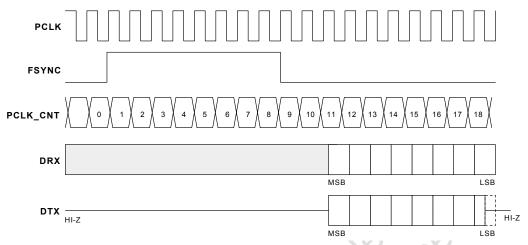

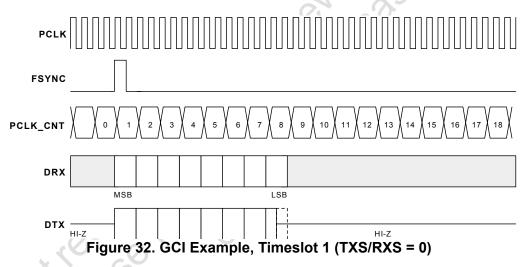

Figure 8. PCM Highway Interface Timing Diagram

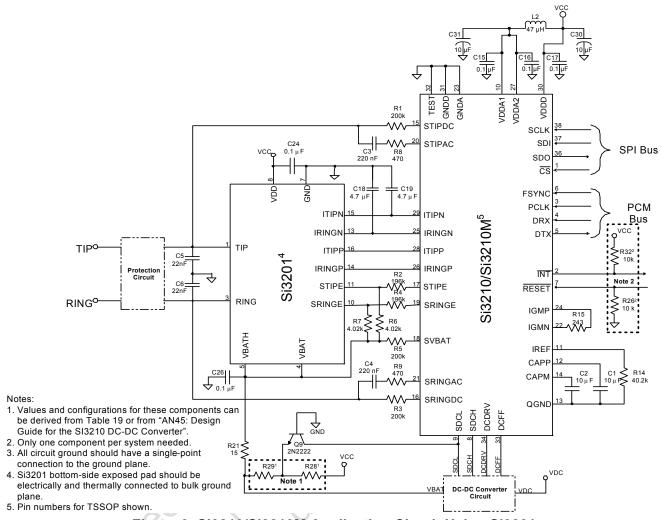

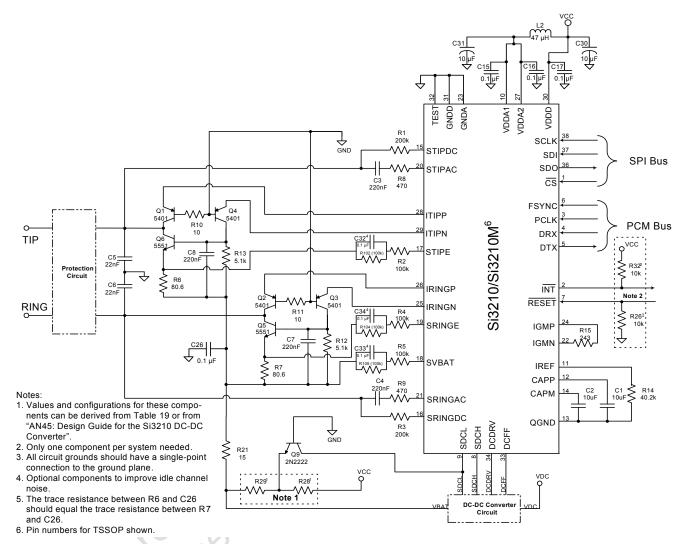

Figure 9. Si3210/Si3210M Application Circuit Using Si3201

Table 12. Si3210/Si3210M + Si3201 External Component Values

| Component(s)                                      | Value                                                                                                      | Package | Supplier                                                           |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------|

| C1,C2                                             | 10 μF, 6 V Ceramic or 16 V Low Leakage<br>Electrolytic, ±20%                                               | Radial  | Murata, Nichicon URL1C100MD                                        |

| C3,C4                                             | 220 nF, 100 V, X7R, ±20%                                                                                   | 1812    | Murata, Johanson, Novacap, Venkel                                  |

| C5,C6                                             | 22 nF, 100 V, X7R, ±20%                                                                                    | 1206    | Murata, Johanson, Novacap, Venkel                                  |

| C15,C16,C17,C24                                   | 0.1 μF, 6 V, Y5V, ±20%                                                                                     | 603     | Murata, Johanson, Novacap, Venkel                                  |

| C18,C19                                           | 4.7 μF, ceramic, 6 V, X7R, ±20%                                                                            | 1206    | Murata, Johanson, Novacap, Venkel                                  |

| C26                                               | 0.1 μF, 100 V, X7R, ±20%                                                                                   | 1210    | Murata, Johanson, Novacap, Venkel                                  |

| C30,C31                                           | 10 μF, 10 V, Electrolytic, ±20%                                                                            | Radial  | Panasonic                                                          |

| L2                                                | 47 μH, 150 mA                                                                                              | SMD     | Coilcraft                                                          |

| R1 <sup>1</sup> ,R3 <sup>1</sup> ,R5 <sup>1</sup> | 200 kΩ, 1/10 W, ±1%                                                                                        | 805     | 5                                                                  |

| R2 <sup>1</sup> ,R4 <sup>1</sup>                  | 196 kΩ, 1/10 W, ±1%                                                                                        | 805     | 0                                                                  |

| R6,R7                                             | 4.02 kΩ, 1/10 W, ±1%                                                                                       | 805     |                                                                    |

| R8,R9                                             | 470 Ω, 1/10 W, ±1%                                                                                         | 805     |                                                                    |

| R14                                               | 40.2 kΩ, 1/10 W, ±1%                                                                                       | 805     | \·                                                                 |

| R15                                               | 243 Ω, 1/10 W, ±1%                                                                                         | 805     |                                                                    |

| R21                                               | 15 Ω, 1/4 W, ±5%                                                                                           | 805     |                                                                    |

| R26 <sup>2</sup>                                  | 10 kΩ, 1/10 W, ±1%                                                                                         | 805     |                                                                    |

| R28,R29                                           | 1/10 W, 1% (See "AN45: Design Guide for<br>the Si3210 DC-DC Converter" or Table 19<br>for value selection) | 805     |                                                                    |

| R32 <sup>2</sup>                                  | 10 kΩ, 1/10 W, ±5%                                                                                         | 805     |                                                                    |

| Q9                                                | 60 V, General Purpose Switching NPN                                                                        | SOT-23  | ON Semi MMBT2222ALT1; Central<br>Semi CMPT2222A; Zetex<br>FMMT2222 |

# Notes:

- These resistors must be in an 0805 or larger package.

- 2. Only one component per system needed.

- 1. Values and configurations for these components can be derived from "AN45: Design Guide for the Si3210 DC-DC Converter" or Table 21.

- 2. Voltage rating for C14 and C25 must be greater than VDC.

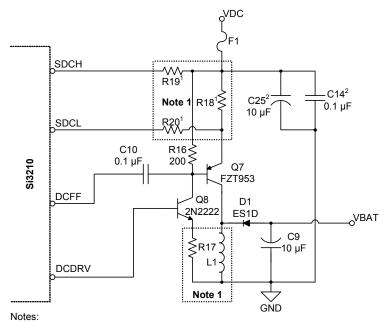

actor DC-DC ( Figure 10. Si3210 BJT/Inductor DC-DC Converter Circuit

Table 13. Si3210 BJT/Inductor DC-DC Converter Component Values

| Component(s) | Value                                                                | Package      | Supplier                                                                                                              |

|--------------|----------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------|

| C9           | 10 μF, 100 V, Electrolytic, ±20%                                     | Radial       | Panasonic                                                                                                             |

| C10          | 0.1 μF, 50 V, X7R, ±20%                                              | 1210         | Murata, Johanson, Novacap, Venkel                                                                                     |

| C14*         | 0.1 μF, X7R, ±20%                                                    | 1210         | Murata, Johanson, Novacap, Venkel                                                                                     |

| C25*         | 10 μF, Electrolytic, ±20%                                            | Radial       | Panasonic                                                                                                             |

| R16          | 200 Ω, 1/10 W, ±5%                                                   | 805          |                                                                                                                       |

| R17          | 1/10 W, ±5% (See AN45 or Table 21 for value selection)               | 805          | , dila                                                                                                                |

| R18          | 1/4 W, ±5% (See AN45 or Table 21 for value selection)                | 1206         | 3000                                                                                                                  |

| R19,R20      | 1/10 W, ±1% (See AN45 or Table 21 for value selection)               | 805          | 000                                                                                                                   |

| F1           | Fuse                                                                 | SMD          | Belfuse SSQ Series                                                                                                    |

| D1           | Ultra Fast Recovery 200 V, 1A Rectifier                              | DO214-<br>AA | General Semi ES1D; Central Semi CMR1U-02                                                                              |

| L1           | 1 A, Shielded Inductor<br>(See AN45 or Table 21 for value selection) | SMD          | API Delevan SPD127 series, Sumida<br>CDRH127 series, Datatronics DR340<br>1 series, Coilcraft DS5022, TDK<br>SLF12565 |

| Q7           | 120 V, High Current Switching PNP                                    | SOT-223      | Zetex FZT953, FZT955, ZTX953,<br>ZTX955; Sanyo 2SA1552                                                                |

| Q8           | 60 V, General Purpose Switching NPN                                  | SOT-23       | ON Semi MMBT2222ALT1,<br>MPS2222A; Central Semi<br>CMPT2222A; Zetex FMMT2222                                          |

|              | ting of this device must be greater than V <sub>DC</sub> .           |              |                                                                                                                       |

|              | otiese in dis                                                        |              |                                                                                                                       |

Notes:

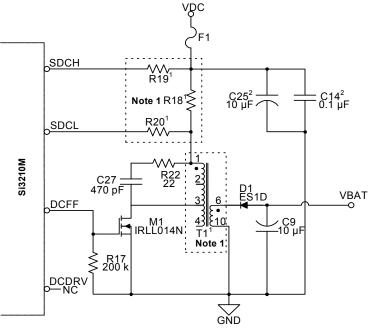

Figure 11. Si3210M MOSFET/Transformer DC-DC Converter Circuit

Values and configurations for these components can be derived from AN45 or Table 20.

<sup>2.</sup> Voltage rating for C14 and C25 must be greater than VDC.

Table 14. Si3210M MOSFET/Transformer DC-DC Converter Component Values

| Component(s)                                                                | Value                                                                                                      | Package | Supplier                                                                       |  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------|--|

| C9                                                                          | 10 μF, 100 V, Electrolytic, ±20%                                                                           | Radial  | Panasonic                                                                      |  |

| C14*                                                                        | 0.1 μF, X7R, ±20%                                                                                          | 1210    | Murata, Johanson, Novacap, Venkel                                              |  |

| C25*                                                                        | 10 μF, Electrolytic, ±20%                                                                                  | Radial  | Panasonic                                                                      |  |

| C27                                                                         | 470 pF, 100 V, X7R, ±20%                                                                                   | 1206    | Murata, Johanson, Novacap, Venkel                                              |  |

| R17                                                                         | 200 kΩ, 1/10 W, ±5%                                                                                        | 805     |                                                                                |  |

| R18                                                                         | 1/4 W, ±5% (See "AN45: Design Guide for<br>the Si3210 DC-DC Converter" or Table 20<br>for value selection) | 1206    | ing.                                                                           |  |

| R19,R20                                                                     | 1/10 W, ±1% (See AN45 or Table 20 for value selection)                                                     | 805     | 5000                                                                           |  |

| R22                                                                         | 22 Ω, 1/10 W, ±5%                                                                                          | 805     | 0                                                                              |  |

| F1                                                                          | Fuse                                                                                                       | SMD     | Belfuse SSQ Series                                                             |  |

| D1                                                                          | Ultra Fast Recovery 200 V, 1 A Rectifier                                                                   | D214-AA | General Semi ES1D; Central Semi<br>CMR1U-02                                    |  |

| T1                                                                          | Power Transformer                                                                                          | SMD     | Coiltronic CTX01-15275;<br>Datatronics SM76315;<br>Midcom 31353R-02            |  |

| M1                                                                          | 100 V, Logic Level Input MOSFET                                                                            | SOT-223 | Intl Rect. IRLL014N; Intersil<br>HUF76609D3S; ST Micro<br>STD5NE10L, STN2NE10L |  |

| *Note: Voltage rating                                                       | g of this device must be greater than V <sub>DC</sub> .                                                    |         |                                                                                |  |

| *Note: Voltage rating of this device must be greater than V <sub>DC</sub> . |                                                                                                            |         |                                                                                |  |

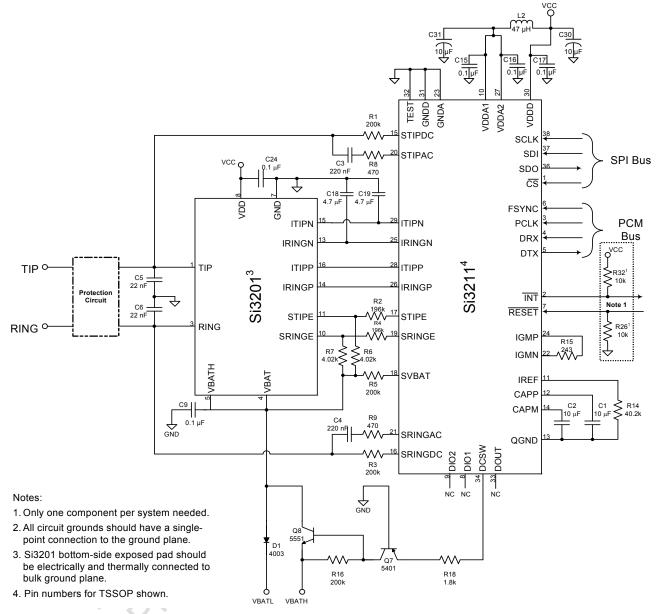

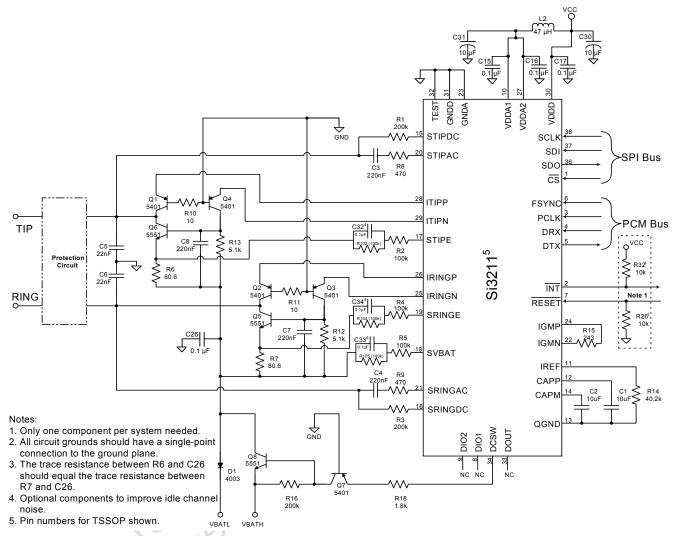

Figure 12. Si3211 Typical Application Circuit Using Si3201

Table 15. Si3211 + Si3201 External Component Values

| Component(s)                                                        | Value                                                         | Package | Supplier                          |

|---------------------------------------------------------------------|---------------------------------------------------------------|---------|-----------------------------------|

| C1,C2                                                               | 10 μF, 6 V Ceramic or 16 V, Low-Leakage<br>Electrolytic, ±20% | Radial  | Murata, Nichicon URL1C100MD       |

| C3,C4                                                               | 220 nF, 100 V, X7R, ±20%                                      | 1812    | Murata, Johanson, Novacap, Venkel |

| C5,C6                                                               | 22 nF, 100 V, X7R, ±20%                                       | 1206    | Murata, Johanson, Novacap, Venkel |

| C9                                                                  | 0.1 μF, 100 V, X7R, ±20%                                      | 1210    | Murata, Johanson, Novacap, Venkel |

| C15,C16,C17,C24                                                     | 0.1 μF, 6 V, Y5V, ±20%                                        | 1206    | Murata, Johanson, Novacap, Venkel |

| C18,C19                                                             | 4.7 μF Ceramic, 6 V, X7R, ±20%                                | 1206    | Murata, Johanson, Novacap, Venkel |

| C30,C31                                                             | 10 μF, 10 V, Electrolytic, ±20%                               | Radial  | Panasonic                         |

| L2                                                                  | 47 μH, 150 mA                                                 | SMD     | Coilcraft                         |

| D1                                                                  | 200 V, 1 A Rectifier                                          | MELF    | ON Semi: MRA4003, IN4003          |

| Q7                                                                  | 120 V, PNP, BJT                                               | SOT-89  | ON Semi: 2N5401                   |

| Q8                                                                  | 120 V, NPN, BJT                                               | SOT-223 | ON Semi: 2N5551                   |

| R1 <sup>1</sup> ,R3 <sup>1</sup> ,R5 <sup>1</sup> ,R16 <sup>1</sup> | 200 kΩ, 1/10 W, ±1%                                           | 805     |                                   |

| R2 <sup>1</sup> ,R4 <sup>1</sup>                                    | 196 kΩ, 1/10 W, ±1%                                           | 805     |                                   |

| R6,R7                                                               | 4.02 kΩ, 1/10 W, ±1%                                          | 805     |                                   |

| R8,R9                                                               | 470 Ω, 1/10 W, ±1%                                            | 805     |                                   |

| R14                                                                 | 40.2 kΩ, 1/10 W, ±1%                                          | 805     |                                   |

| R15                                                                 | 243 Ω, 1/10 W, ±1%                                            | 805     |                                   |

| R18                                                                 | 1.8 kΩ, 1/10 W, ±5%                                           | 805     |                                   |

| R26 <sup>2</sup>                                                    | 10 kΩ, 1/10 W, ±1%                                            | 805     |                                   |

| R32 <sup>2</sup>                                                    | 10 kΩ, 1/10 W, ±5%                                            | 805     |                                   |

# Notes:

- 1. These resistors must be in an 0805 or larger package.

- 2. Only one component per system needed.

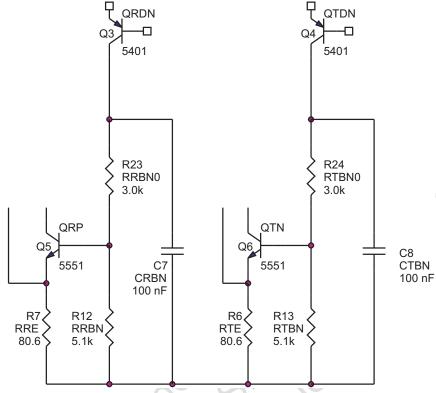

Figure 13. Si3210/Si3210M Typical Application Circuit Using Discrete Components

Table 16. Si3210/Si3210M External Component Values—Discrete Solution

| Component(s)                                                                                                          | Value                                                                                                       | Package | Supplier/Part Number                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------|

| C1,C2                                                                                                                 | 10 μF, 6 V Ceramic or 16 V Low-Leakage<br>Electrolytic, ±20%                                                | Radial  | Murata, Panasonic, Nichicon<br>URL1C100MD                                                                     |

| C3,C4                                                                                                                 | 220 nF, 100 V, X7R, ±20%                                                                                    | 1812    | Murata, Johanson, Novacap, Venkel                                                                             |

| C5,C6                                                                                                                 | 22 nF, 100 V, X7R, ±20%                                                                                     | 1206    | Murata, Johanson, Novacap, Venkel                                                                             |

| C7,C8                                                                                                                 | 220 nF, 50 V, X7R, ±20%                                                                                     | 1812    | Murata, Johanson, Novacap, Venkel                                                                             |

| C15,C16,C17                                                                                                           | 0.1 μF, 6 V, Y5V, ±20%                                                                                      | 603     | Murata, Johanson, Novacap, Venkel                                                                             |

| C26                                                                                                                   | 0.1 μF, 100 V, X7R, ±20%                                                                                    | 1210    | Murata, Johanson, Novacap, Venkel                                                                             |

| C30,C31                                                                                                               | 10 μF, 10 V, Electrolytic, ±20%                                                                             | Radial  | Panasonic                                                                                                     |

| C32,C33,C34                                                                                                           | 0.1 μF, 50 V, ±20%                                                                                          | 805     | Venkel                                                                                                        |

| L2                                                                                                                    | 47 μH, 150 mA                                                                                               | SMD     | Coilcraft                                                                                                     |

| Q1,Q2,Q3,Q4                                                                                                           | 120 V, PNP, BJT                                                                                             | SOT-23  | Central Semi CMPT5401; ON Semi<br>MMBT5401LT1, 2N5401; Zetex<br>FMMT5401;<br>Fairchild 2N5401; Samsung 2N5401 |

| Q5,Q6                                                                                                                 | 120 V, NPN, BJT                                                                                             | SOT-223 | Central Semi CZT5551, ON Semi<br>2N5551;<br>Fairchild 2N5551; Phillips 2N5551                                 |

| Q9                                                                                                                    | NPN General Purpose BJT                                                                                     | SOT-23  | ON Semi MMBT2222ALT1, MPS2222A;<br>Central Semi CMPT2222A; Zetex<br>FMMT2222                                  |

| R1 <sup>1</sup> , R3 <sup>1</sup>                                                                                     | 200 kΩ, 1/10 W, ±1%                                                                                         | 805     |                                                                                                               |

| R2 <sup>1</sup> , R4 <sup>1</sup> , R5 <sup>1</sup> ,<br>R102 <sup>1</sup> , R104 <sup>1</sup> ,<br>R105 <sup>1</sup> | 100 kΩ, 1/10 W, ±1%                                                                                         | 805     |                                                                                                               |

| R6,R7                                                                                                                 | 80.6 Ω, 1/4 W, ±1%                                                                                          | 1210    |                                                                                                               |

| R8,R9                                                                                                                 | 470 Ω, 1/10 W, ±1%                                                                                          | 805     |                                                                                                               |

| R10,R11                                                                                                               | 10 Ω, 1/10 W, ±5%                                                                                           | 805     |                                                                                                               |

| R12,R13                                                                                                               | 5.1 kΩ, 1/10 W, ±5%                                                                                         | 805     |                                                                                                               |

| R14                                                                                                                   | 40.2 kΩ, 1/10 W, ±1%                                                                                        | 805     |                                                                                                               |

| R15                                                                                                                   | 243 Ω, 1/10 W, ±1%                                                                                          | 805     |                                                                                                               |

| R21                                                                                                                   | 15 Ω, 1/4 W, ±1%                                                                                            | 805     |                                                                                                               |

| R26 <sup>2</sup>                                                                                                      | 10 kΩ, 1/10 W, ±1%                                                                                          | 805     |                                                                                                               |

| R28,R29                                                                                                               | 1/10 W, ±1% (See "AN45: Design Guide for the Si3210/15/16 DC-DC Converter" or Table 19 for value selection) | 805     |                                                                                                               |

| R32 <sup>2</sup>                                                                                                      | 10 kΩ, 1/10 W, ±5%                                                                                          | 805     |                                                                                                               |

# Notes:

- 1. These resistors must be in 0805 or larger package.

- 2. Only one component per system needed.

Figure 14. Si3211 Typical Application Circuit Using Discrete Solution

Table 17. Si3211 External Component Values—Discrete Solution

| Component(s)                                                                                                          | Value                                                        | Package | Supplier/Part Number                                                     |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------|--------------------------------------------------------------------------|

| C1,C2                                                                                                                 | 10 μF, 6 V Ceramic or 16 V Low Leakage<br>Electrolytic, ±20% | Radial  | Murata, Panasonic, Nichicon<br>URL1C100MD                                |

| C3,C4                                                                                                                 | 220 nF, 100 V, X7R, ±20%                                     | 1812    | Murata, Johanson, Novacap, Venkel                                        |

| C5,C6                                                                                                                 | 22 nF, 100 V, X7R, ±20%                                      | 1206    | Murata, Johanson, Novacap, Venkel                                        |

| C7,C8                                                                                                                 | 220 nF, 50 V, X7R, ±20%                                      | 1812    | Murata, Johanson, Novacap, Venkel                                        |

| C9                                                                                                                    | 0.1 μF, 100 V, X7R, ±20%                                     | 1210    | Panasonic                                                                |

| C15,C16,C17                                                                                                           | 0.1 μF, 6 V, Y5V, ±20%                                       | 603     | Murata, Johanson, Novacap, Venkel                                        |

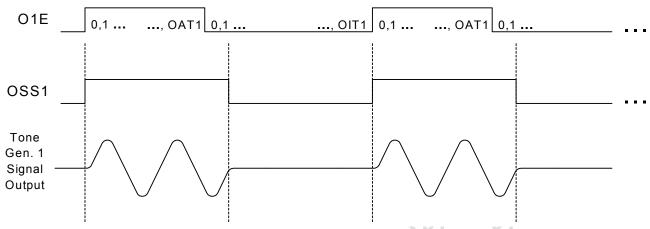

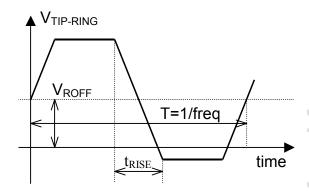

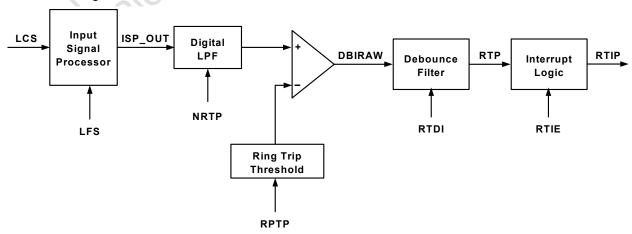

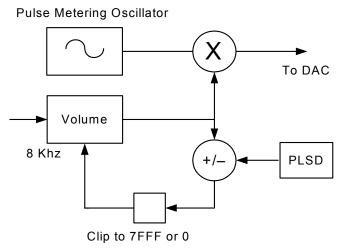

| C30,C31                                                                                                               | 10 μF, 10 V, X7R, ±20%                                       | Radial  | Panasonic                                                                |